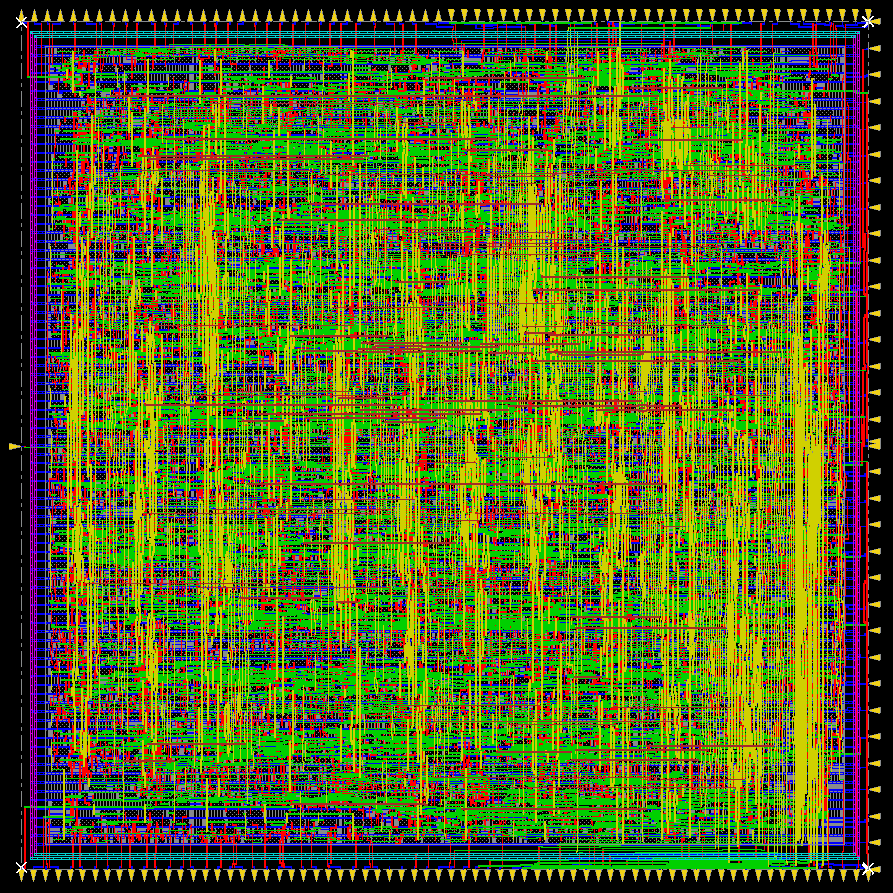

3-Stage RISC-V CPU

Implemented complete RISC-V ISA and 4KB direct mapped cache in Verilog HDL for SKY130 PDK. Optimized performance with 3-stage pipelining and forwarding mechanisms. Simulated and debugged with Synopsys VCS, synthesized using Cadence Genus, and routed with Cadence Innovus.

Analyzed power (Cadence Voltus), performance, and area using industry-standard VLSI EDA tools. Implemented 4KB direct mapped cache with SRAM hard macros and wrote automated testbenches for critical subsystems including ALU. Full ASIC implementation using SKY130 process technology.

← Back to Timeline